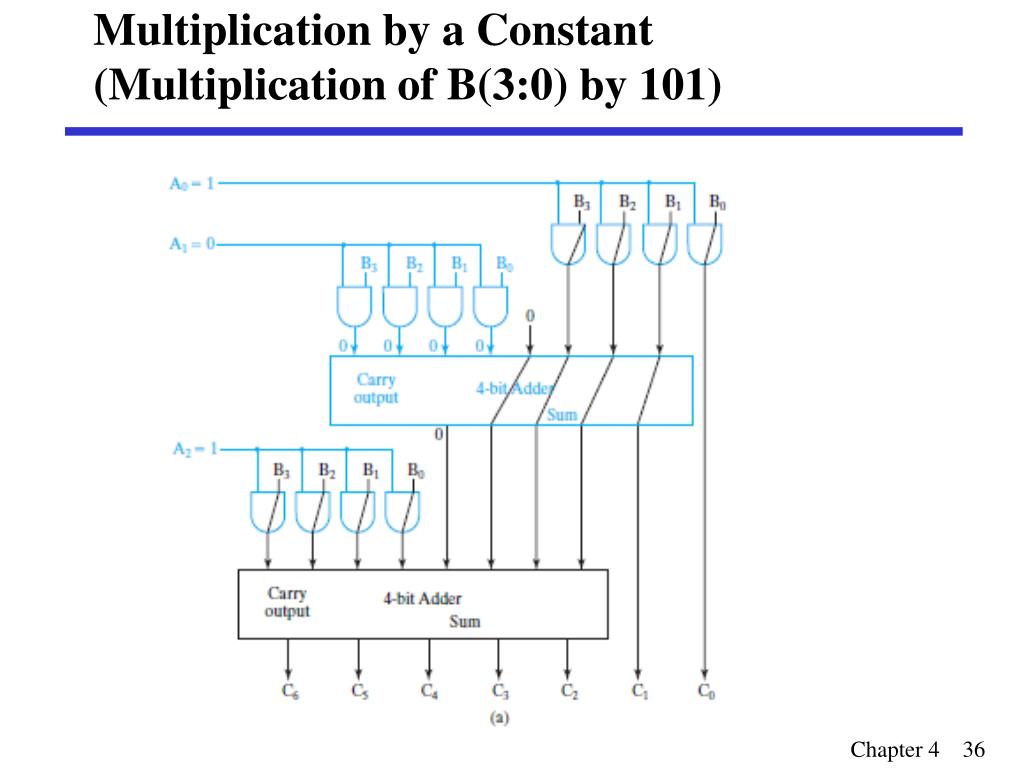

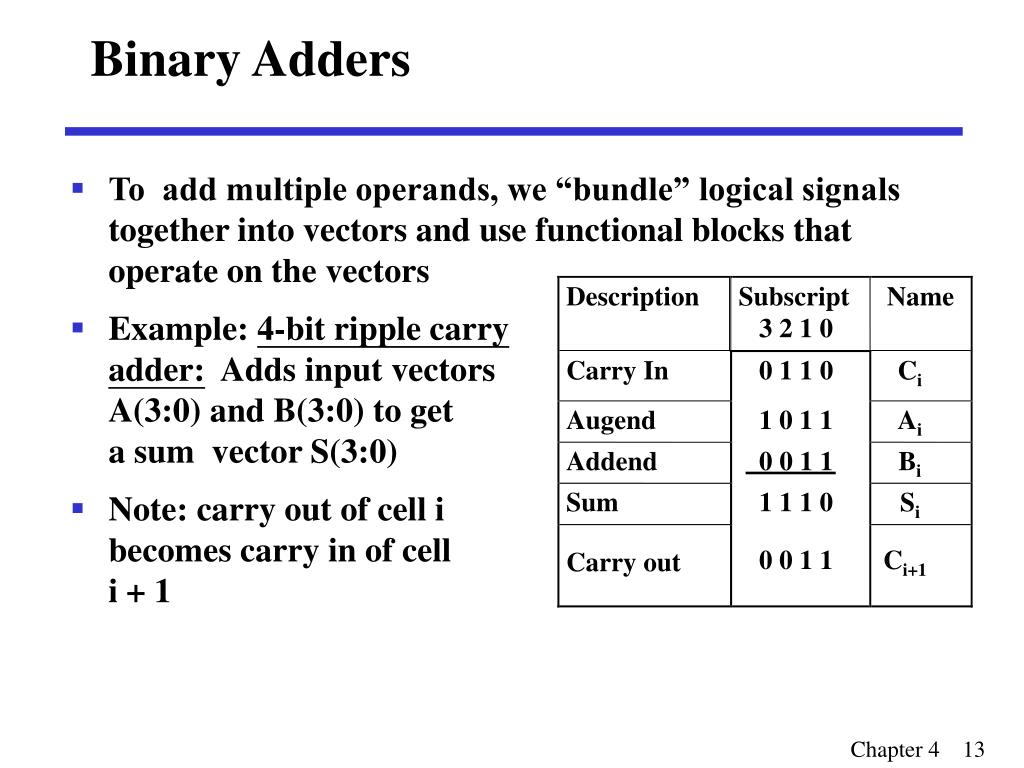

Simple Examples Using 4 Bit Parallel Adder As Building

Standard Product Components And Design Techniques For

Adder S Vlsi Embedded Projects

Microscope Photograph Of C Mos Reversible Carry Look Ahead

Department Of Electrical And Electronics Engineering

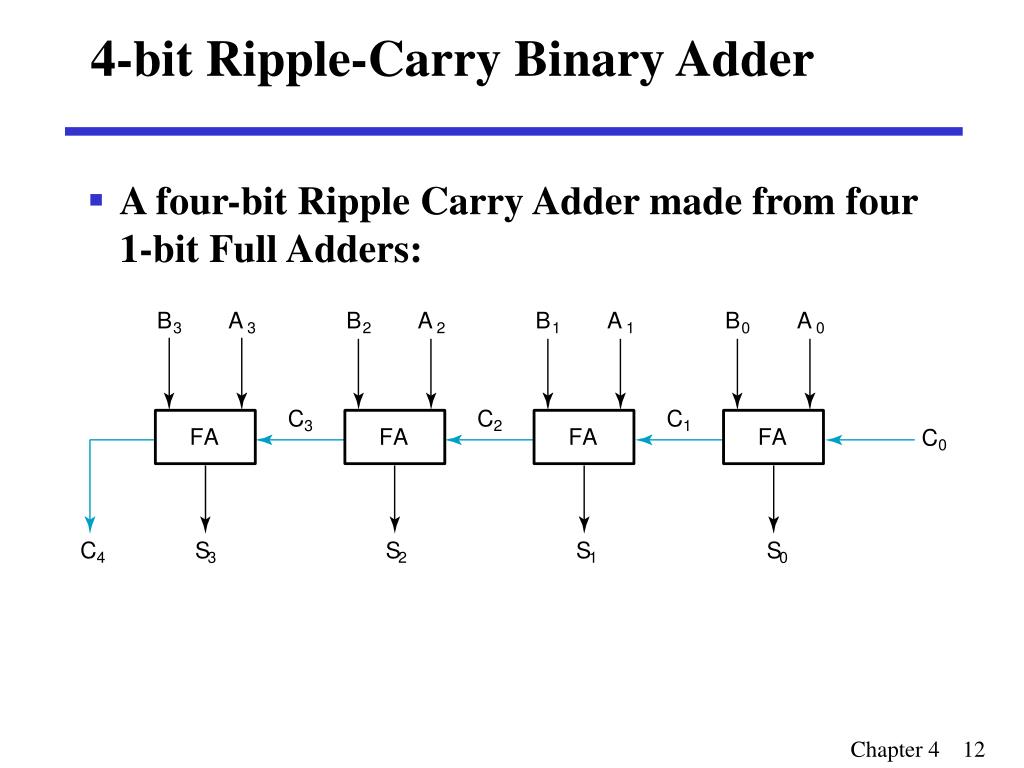

Ppt Overview Powerpoint Presentation Id 5073266

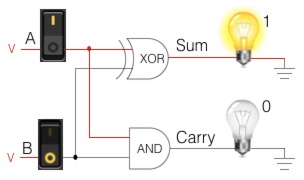

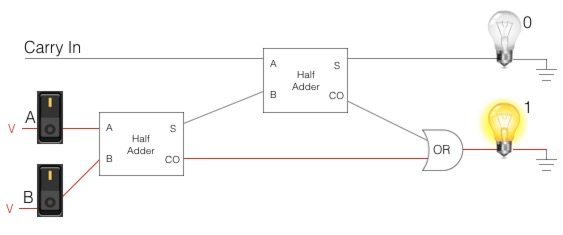

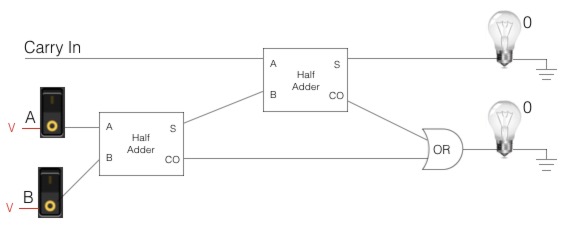

How To Design A Full Adder Using Two Half Adders Quora

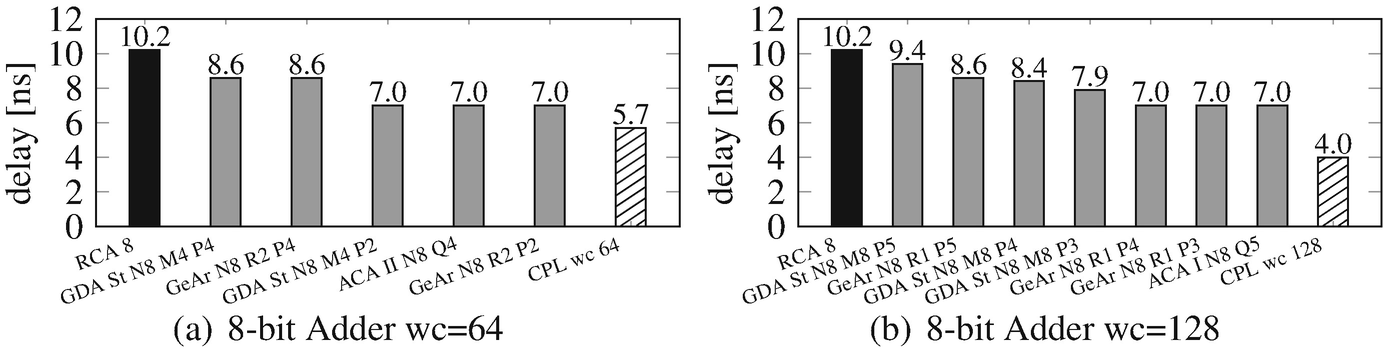

Approximate Computing With Stochastic Transistors X2019

Low Power Approximate Unsigned Multipliers With Configurable

Lab 2 Report Objective S In This Lab The Students

Amazon Com Black Adder Special Rowan Atkinson Tony

Digital Electronic Experiments Computer Principles

4 Bit Parallel Adder C 5 C 1 X 2 X 1 Y 4 Y 3 S 4 S 3 S 2 S 1

Enkuzmenko Eric Kuzmenko

Untitled

Electro Optic Ripple Carry Adder In Integrated Silicon

Department Of Electrical Engineering Laboratory Manual Ee

Jk Flip Flop Truth Table Characteristic Table Waveform

Design And Analysis Of Approximate Compressors For

Design And Implementation Of 16 Bit Carry Look Ahead Adder

Dtn 6 6 19 By Dailytimes Issuu

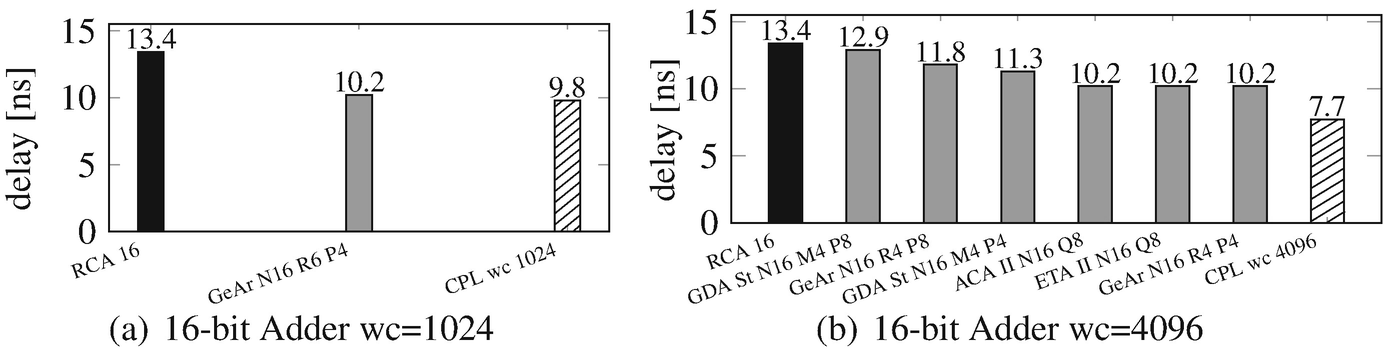

Approximate Hardware Generation Using Formal Techniques

Uc Santa Cruz

4 Bit Parallel Adder C 5 C 1 X 2 X 1 Y 4 Y 3 S 4 S 3 S 2 S 1

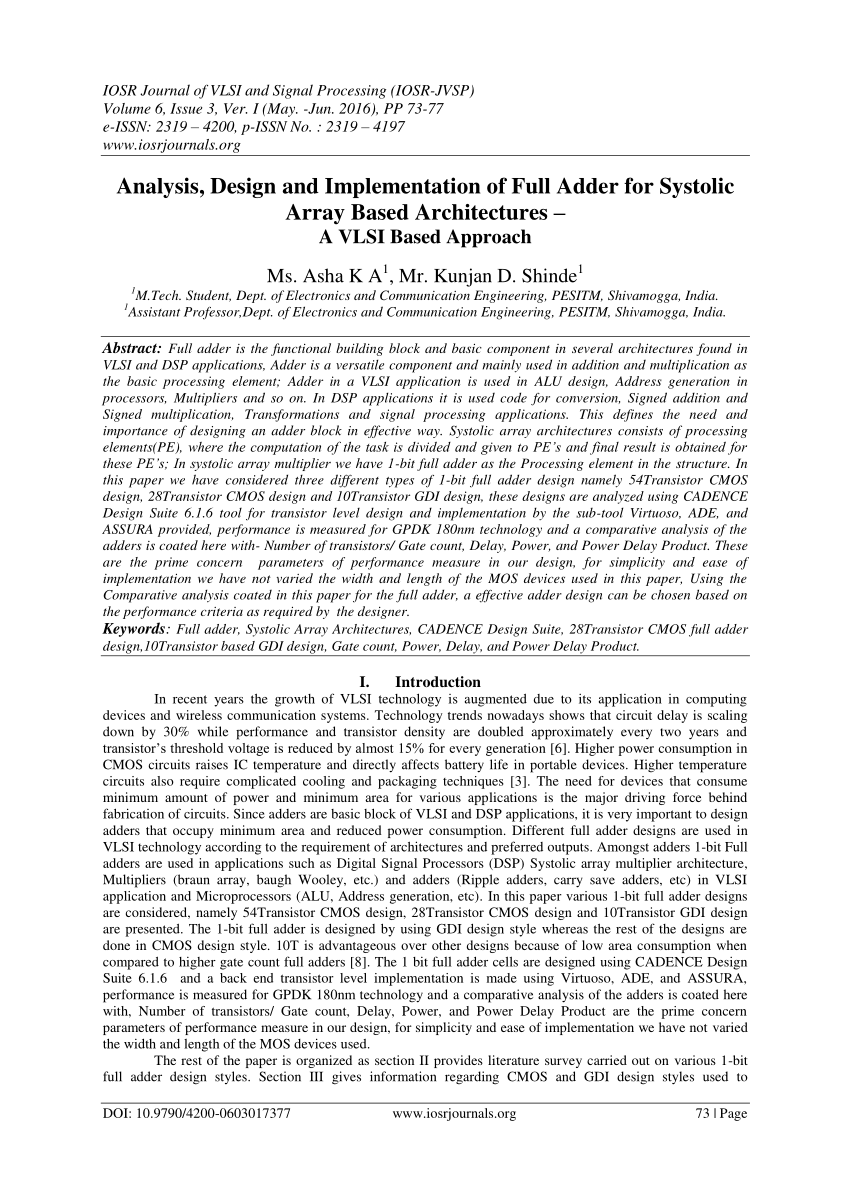

Pdf Analysis Design And Implementation Of Full Adder For

Department Of Electrical And Electronics Engineering

Department Of Electrical Engineering Laboratory Manual Ee

Approximate Computing With Stochastic Transistors X2019

239587360 Ee200 Lab Manual

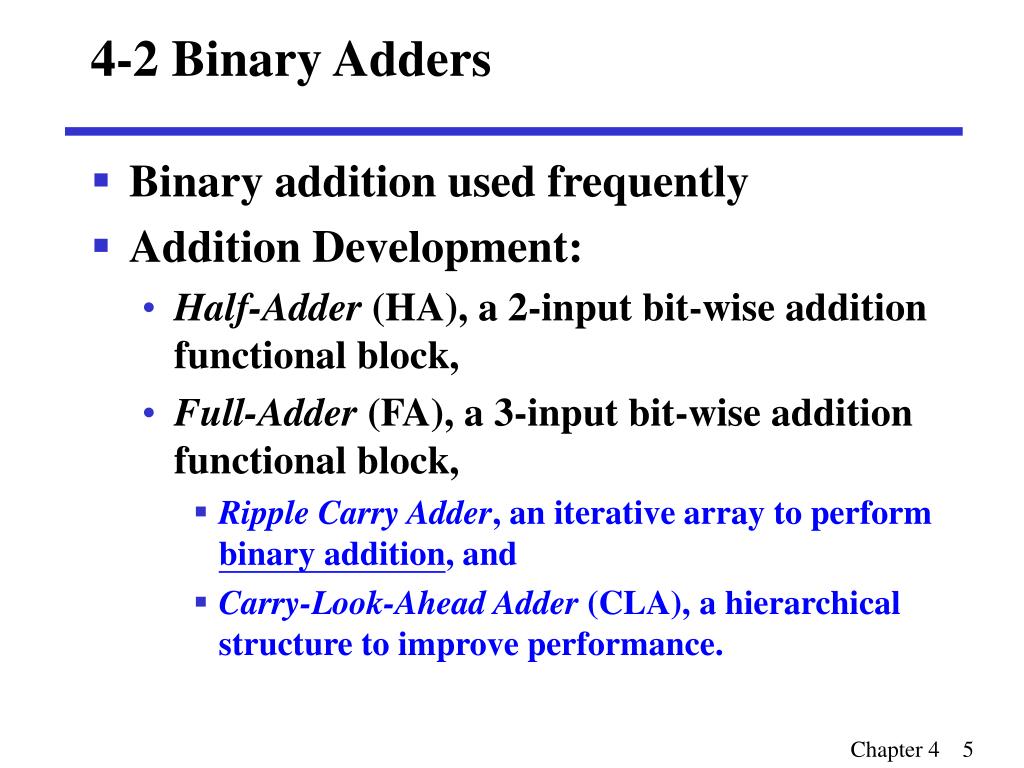

Basics Of The Adder Circuit Know The Code

Gate Array Representation Of Evolved 1 Bit Adder In Fig 2 A

How To Design A Full Adder Using Two Half Adders Quora

Block Diagram Of One Bit Adder With Carry And Conventional

16 Bit Ripple Carry Adder Download Table

Approximate Hardware Generation Using Formal Techniques

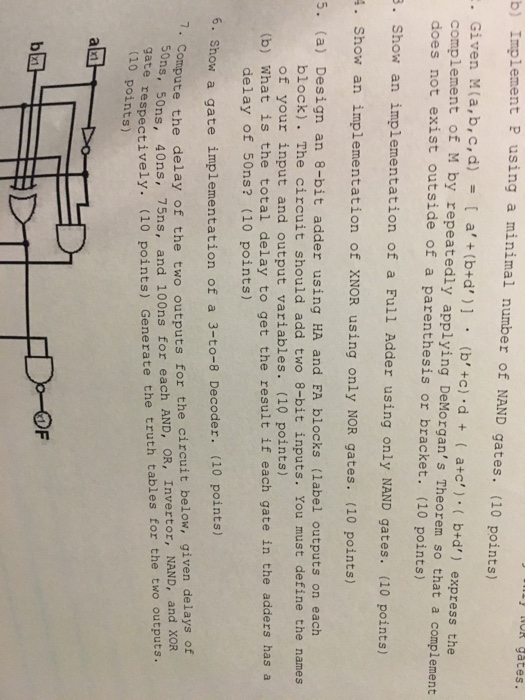

Final Examination

Booth Multiplier Vlsi Embedded Projects

Digital Systems Laboratory Esogu Electrical Electronics

Design And Implementation Of 16 Bit Carry Look Ahead Adder

Satan S Bushel Foundation For Economic Education

Final Examination

Implementation Of High Speed And Low Power Radix 4 8 8 Booth

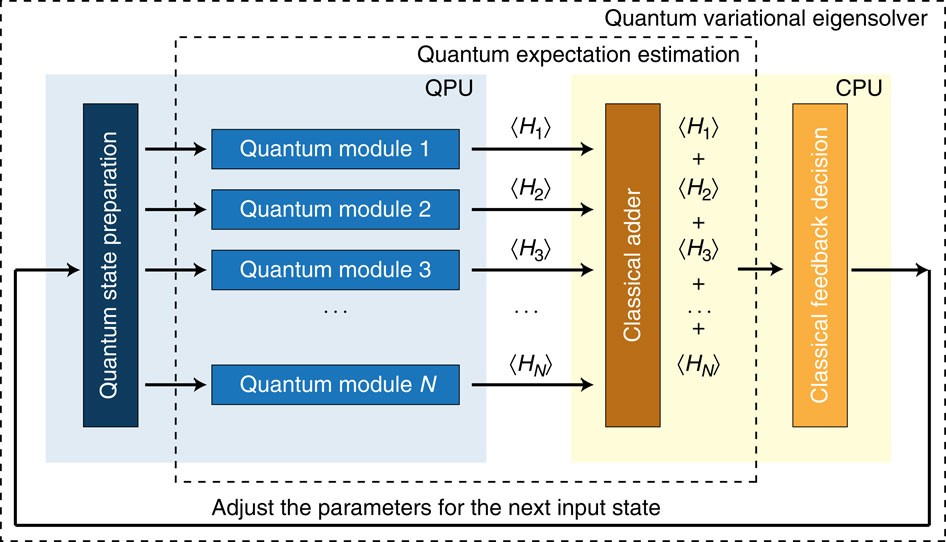

A Variational Eigenvalue Solver On A Photonic Quantum

Cse120 Simulation Lab 2 Introduction In This Lab The

Design And Analysis Of Approximate Compressors For

Designing And Building The Alu Details Hackaday Io

Untitled

Lab Report 05 Doc Ece 206 Digital Electronics Date Of

Simple Examples Using 4 Bit Parallel Adder As Building

Approximate Computing In Coarse Grained Reconfigurable

Digital Systems Laboratory Pdf

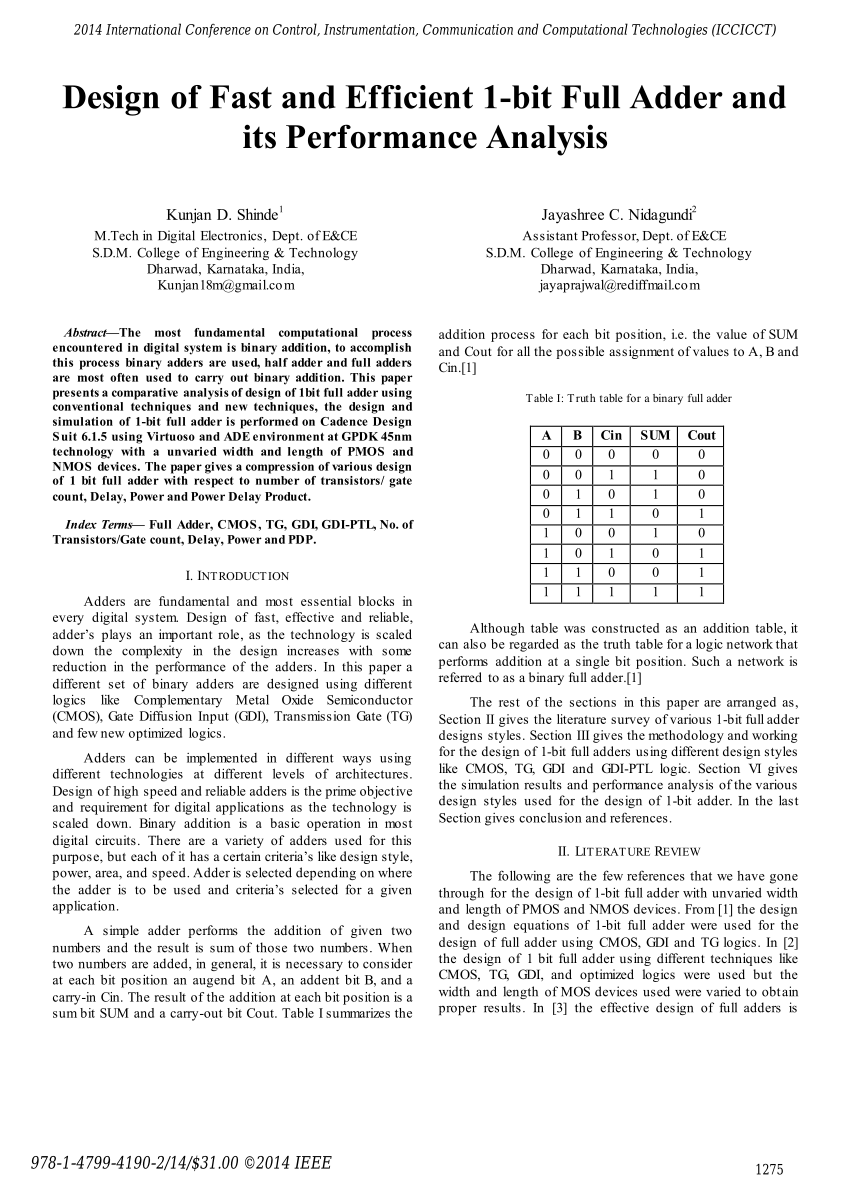

Pdf Design Of Fast And Efficient 1 Bit Full Adder And Its

239587360 Ee200 Lab Manual

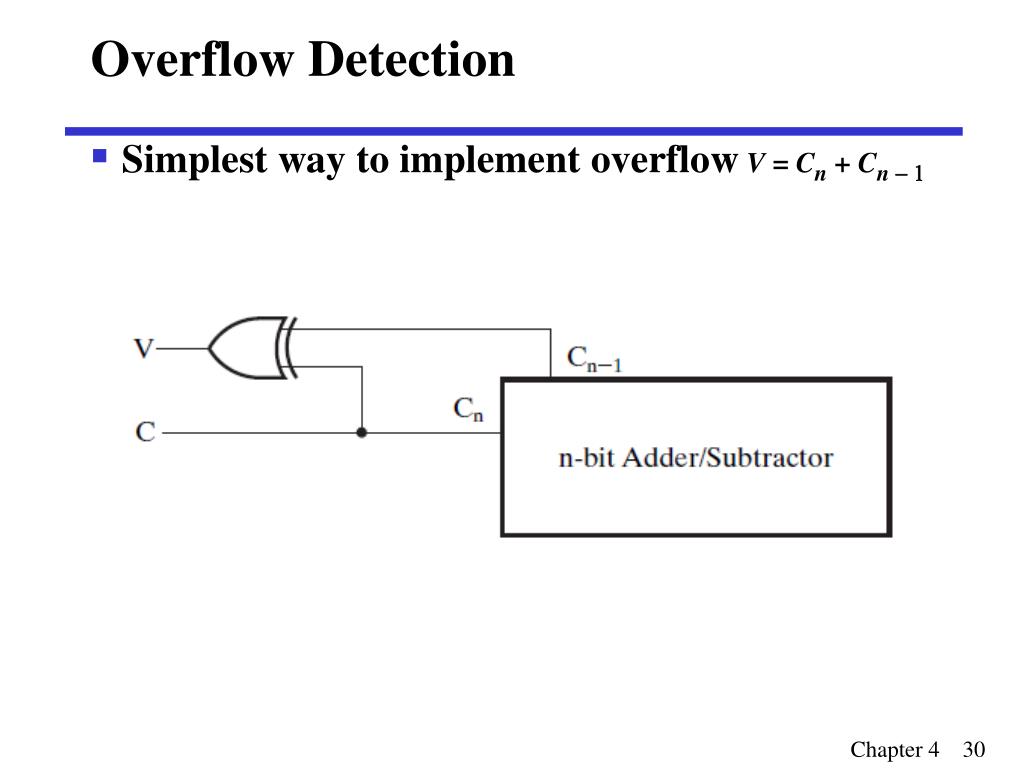

Ppt Overview Powerpoint Presentation Id 5073266

Department Of Electrical And Electronics Engineering

Architecture Of Proposed 4 Bit Reversible Carry Look Ahead

Pdf Laboratory Manual Ee 200 Digital Design Sravan

Implementation Of High Speed And Low Power Radix 4 8 8 Booth

Approximate Computing With Stochastic Transistors X2019

Fundamentals Of Logic Design Pages 101 150 Text Version

How To Design A Full Adder Using Two Half Adders Quora

An Analytical Framework For Evaluating The Error

Astor Bidet Fresh Water Spray Non Electric Mechanical Bidet Toilet Seat Attachment Cb 1000

Ppt Overview Powerpoint Presentation Id 5073266

Table 8 Thaoduocthanghoa Info

New Metrics For The Reliability Of Approximate And

Digital Systems Laboratory Pdf

Basics Of The Adder Circuit Know The Code

For The Cra We Use 16 Full Adders Each Full Adder Takes 3

The Babees Book By Dr F J Furnivall A Project

Untitled

Fundamentals Of Logic Design Pages 101 150 Text Version

Low Power Approximate Unsigned Multipliers With Configurable

Fundamentals Of Logic Design Pages 101 150 Text Version

Memory Address Register An Overview Sciencedirect Topics

Uc Santa Cruz

Approximate Computing With Stochastic Transistors X2019

Basics Of The Adder Circuit Know The Code

Department Of Electrical And Electronics Engineering

An Analytical Framework For Evaluating The Error

Digital Systems Laboratory Pdf

Lab08 Ece1551 Digital Logic Lab 2 Bit Adder 1 Bit Adder

Fest Of Tails San Antonio Parks Foundation

Department Of Electrical Engineering Laboratory Manual Ee

Table 8 Thaoduocthanghoa Info

Untitled

Laboratory Manual Ee 200 Digital Design

Ppt Overview Powerpoint Presentation Id 5073266

Solved Implement P Using A Minimal Number Of Nand Gates

Electro Optic Ripple Carry Adder In Integrated Silicon

Approximate Computing With Stochastic Transistors X2019

Improved Design Of High Performance Parallel Decimal Multipliers

Design For Realizing An All Optical Terahertz Wave Half

Fundamentals Of Logic Design Pages 101 150 Text Version

Architecture Of Proposed 4 Bit Reversible Carry Look Ahead

Ppt Overview Powerpoint Presentation Id 5073266

Write Truth Table For Output Bits From Your Bit Slice In

Department Of Electrical Engineering Laboratory Manual Ee